본문

HyperLynx SI : Understanding Signal Integrity (1)

Signal Integrity란?

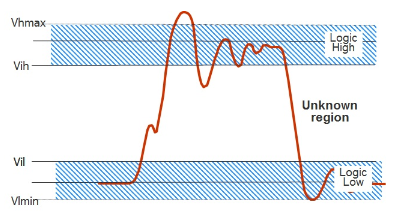

간단히 말하자면, Signal Integrity란 digital 신호의 품질을 측정하는 것을 말합니다. 디지털 신호의 파형은 이상적으로는 구형파이지만, analog 특성이 reflection을 일으킵니다. Reflection은 신호를 왜곡하기 때문에 신호가 기대한 것처럼 깨끗하게 “1”, “0”으로 보이지 않게 됩니다. Signal Integrity 문제로 인해 bit error뿐 아니라 심지어 component 오류를 일으킬 수 있습니다.

More Common Terms & Reading Waveforms

1. Impedance

Impedance는 “SQRT(L/C)”로 계산할 수 있습니다. 임피던스 불연속의 주요 원인은 trace의 폭 변경과 trace의 layer 변경이 있습니다. 그렇기 때문에 trace의 임피던스를 정하는데 있어서 올바르게 정의된 stackup이 매우 중요합니다. Trace가 얇아지거나 plane으로부터 거리가 멀어짐에 따라 impedance는 증가합니다. 임피던스 불연속의 다른 원인에는 via와 component의 input/output impedance가 있습니다.

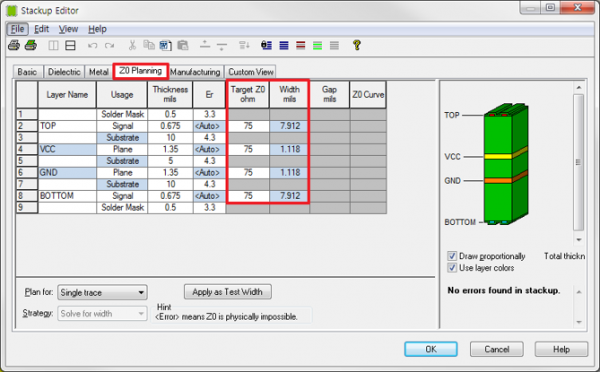

Tip : Impedance planning을 위해 Stackup Editor를 이용하세요.

▷ Setup > Stackup > Edit (Basic and Z0 Planning Tabs)

참고 : [SI] 6. Stackup Editor 활용하기

2. Critical Length

Critical Length는 trace가 transmission line으로 동작하기 시작하는 기준입니다. Critical Length는 driver의 edge rate와 관련이 있습니다. 예전에 잘 동작했던 board에 새로운 부품을 올려놨을 때, SI 문제가 생기는 이유가 바로 이것 때문입니다. 요즘은 edge rate가 빨라지고 있기 때문에 여러분의 board는 transmission line을 가지고 있는 것입니다. Trace의 delay가 edge rate의 10~20% 정도일 때 trace를 transmission line으로 봐야 합니다.

3. Reflection

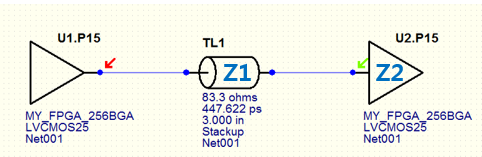

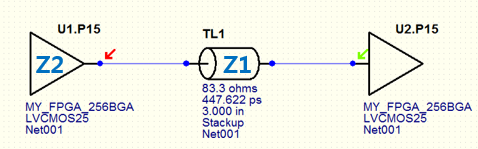

Reflection은 임피던스 불연속에 의해 발생합니다. 반사 계수(reflection의 크기)는 (Z2-Z1)/(Z2+Z1) 공식으로 구할 수 있습니다.

1) Z1 < Z2인 경우(receiver input impedance가 연결된 trace의 임피던스보다 큰 경우), 양의 반사가 발생합니다.

2) Z1 = Z2인 경우(Impedance를 유지하기 위해 layer 변경 시 trace 폭을 변경하거나 termination을 사용한 경우), reflection이 발생하지 않습니다.

3) Z1 > Z2인 경우(driver output impedance가 trace impedance 보다 작은 경우), 음의 Reflection이 발생합니다.

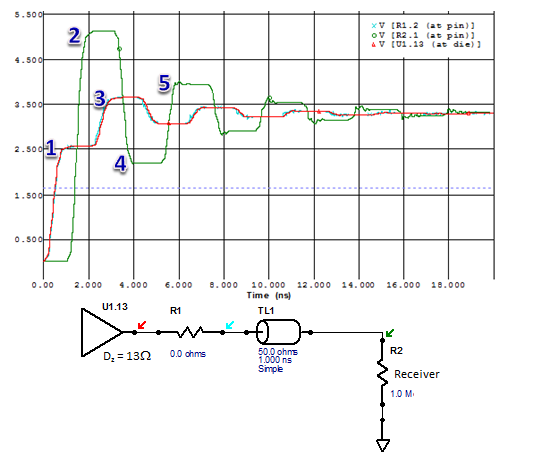

파형을 예측할 수 있다면, 여러분의 설정에 문제가 있는지 더 쉽게 알아낼 수 있습니다.

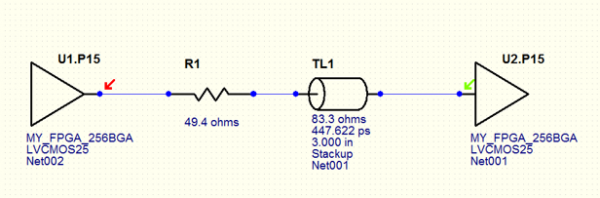

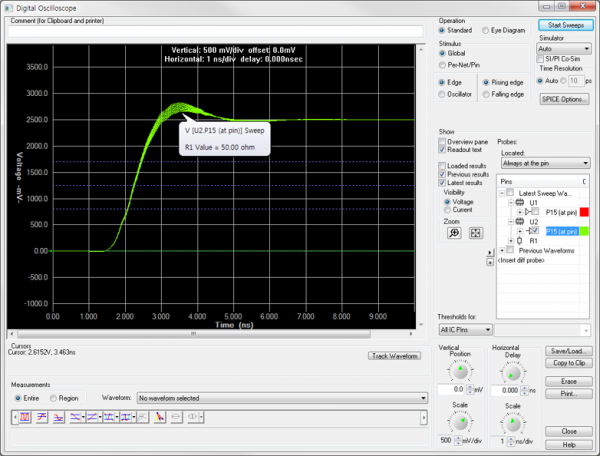

상단의 회로를 보면, probe point를 만들기 위한 0 ohm의 저항과 receiver의 high-impedance를 나타내는 1.0M ohm의 저항이 있는 것을 확인할 수 있습니다. Driver의 output impedance는 ~13ohm 정도 됩니다. 숫자로 표시된 각 파형에 대한 설명은 아래 해당 번호에 설명되어 있습니다.

1. 입사 파는 약 2.57V 정도 됩니다. (output impedance와 line impedance에 의해 전압이 분배됩니다.)

2. 파형이 R2에 도달하면 큰 reflection이 발생합니다.

◦ 위의 회로에서 trace의 지연시간은 1ns이고, 1ns 일 때 R2에서 신호가 전이 됩니다.

◦ 2.57+(2.57(1M-50)/(1M+50)) = 2.57+2.57 = 5.14V

3. 양의 Reflection이 2ns 후에 driver의 뒤쪽에서 발생됩니다.

◦ 2.57+2.57+(2.57(13-50)/(13+50)) = 2.57+2.57-1.477 = 3.66V

4. 3ns 때 음의 reflection이 receiver로 되돌아가서 기존 파형 및 receiver의 reflection과 더해집니다.

◦ 5.14-1.477+(-1.477*((1M-50/(1M+50))=5.14-1.477-1.477=2.189V

5. Reflection은 driver에 도달할 때마다 크기가 줄어들고 극성이 바뀝니다. 결국 ringing은 안정됩니다.

4. Termination

Termination은 impedance matching으로 reflection을 제어할 때 사용됩니다. 가장 흔히 사용되는 termination type은 series termination과 parallel termination이 있습니다.

1) Series Termination : Series Termination은 driver 가까이에 직렬로 배치됩니다. Reflection이 driver로 되돌아올 때, “trace의 impedance”와 “Termination + Driver output impedance”가 매칭되어 reflection은 종결됩니다.

2) Parallel Termination : Parallel Termination은 line 끝에 trace와 impedance 매칭된 저항을 병렬 연결하여 배치합니다.

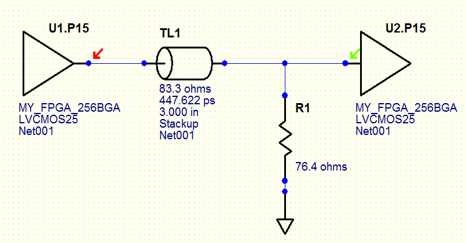

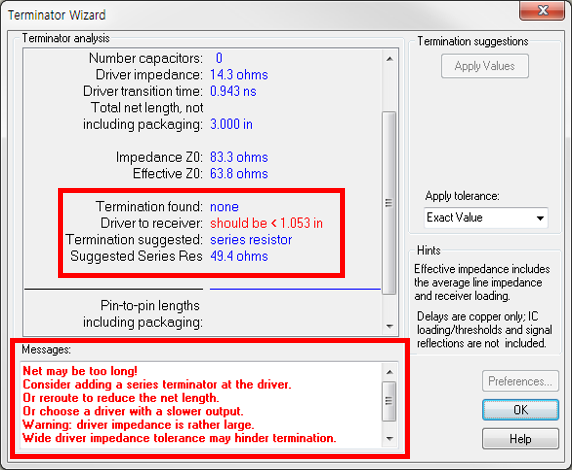

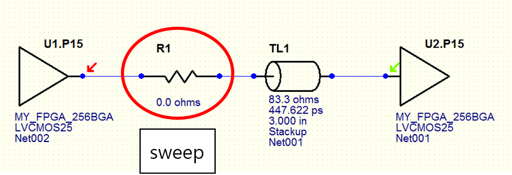

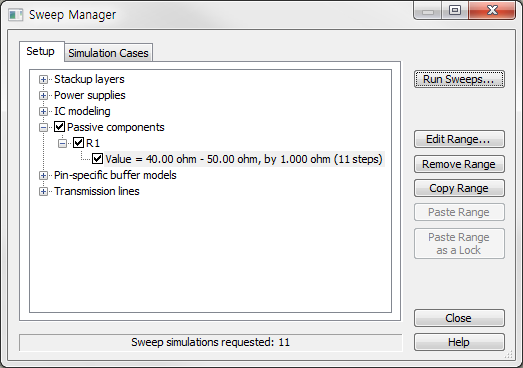

Tip : Terminator Wizard와 Sweep Manager를 이용하여 최적의 termination value를 찾을 수 있습니다.

1) Terminator Wizard

2) Sweep Manager

등록된 댓글이 없습니다.