HyperLynx SI

Overview

오늘날 IC들의 스위칭 속도가 빨라지면서 over/undershoot, ringing, glitching, crosstalk, timing 문제가 발생하고 있습니다. 심지어 낮은 주파수 동작하는 PCB 디자인에서도 signal integrity(신호 무결성) 문제가 발생하고 있습니다. 이러한 signal integrity 문제들로 인해 board의 회로가 제대로 동작하지 않을 수 있습니다. 따라서 제품 설계 시 signal integrity 분석은 필수 과정이 되었으며 HyperLynx SI를 이용하여 PCB 디자인에 대해 빠르고 정확한 signal integrity를 분석할 수 있습니다. HyperLynx SI는 사용 편의성을 높이고 작업 흐름(workflow) 자동화하여 signal integrity 전문가가 요구하는 상세한 모델링과 정확한 시뮬레이션을 지원하면서도 시스템 설계 엔지니어가 복잡한 SI 분석을 쉽게 진행할 수 있도록 도와줍니다.

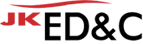

배선 전(Pre-Route) 설계 계획

HyperLynx 스케매틱 에디터(LineSim)를 이용하여 배선 전(Pre-route) SI 시뮬레이션을 진행할 수 있습니다. PCB 설계 전 다양한 적층 구조(stackup)를 평가하고 topology, termination, via 구조, trace 간 간격 등을 최적화하여 어떤 물리적 설계 방법이 가장 적합한 지 결정할 수 있습니다.

IC, trace, via, cable, connector, 수동 소자를 끌어서 놓기(드래그 앤 드롭)로 복잡한 스케매틱을 빠르게 설계하고 시뮬레이션 가능

IC, trace, via, cable, connector, 수동 소자를 끌어서 놓기(드래그 앤 드롭)로 복잡한 스케매틱을 빠르게 설계하고 시뮬레이션 가능

Crosstalk 분석으로 설계 마진과 간격 사이의 균형 조정

Crosstalk 분석으로 설계 마진과 간격 사이의 균형 조정

통합된 2D 및 3D EM solver는 trace, via 및 기타 구조 요소에 대한 매우 정확한 모델을 제공

통합된 2D 및 3D EM solver는 trace, via 및 기타 구조 요소에 대한 매우 정확한 모델을 제공

대화식(interactive) 시뮬레이션을 통해 신호 품질, crosstalk 등에 대한 설계 변경의 영향을 바로 확인 가능

대화식(interactive) 시뮬레이션을 통해 신호 품질, crosstalk 등에 대한 설계 변경의 영향을 바로 확인 가능

Parameter sweep 분석으로 회로 동작에 대한 설계 변수의 영향을 정량화

Parameter sweep 분석으로 회로 동작에 대한 설계 변수의 영향을 정량화

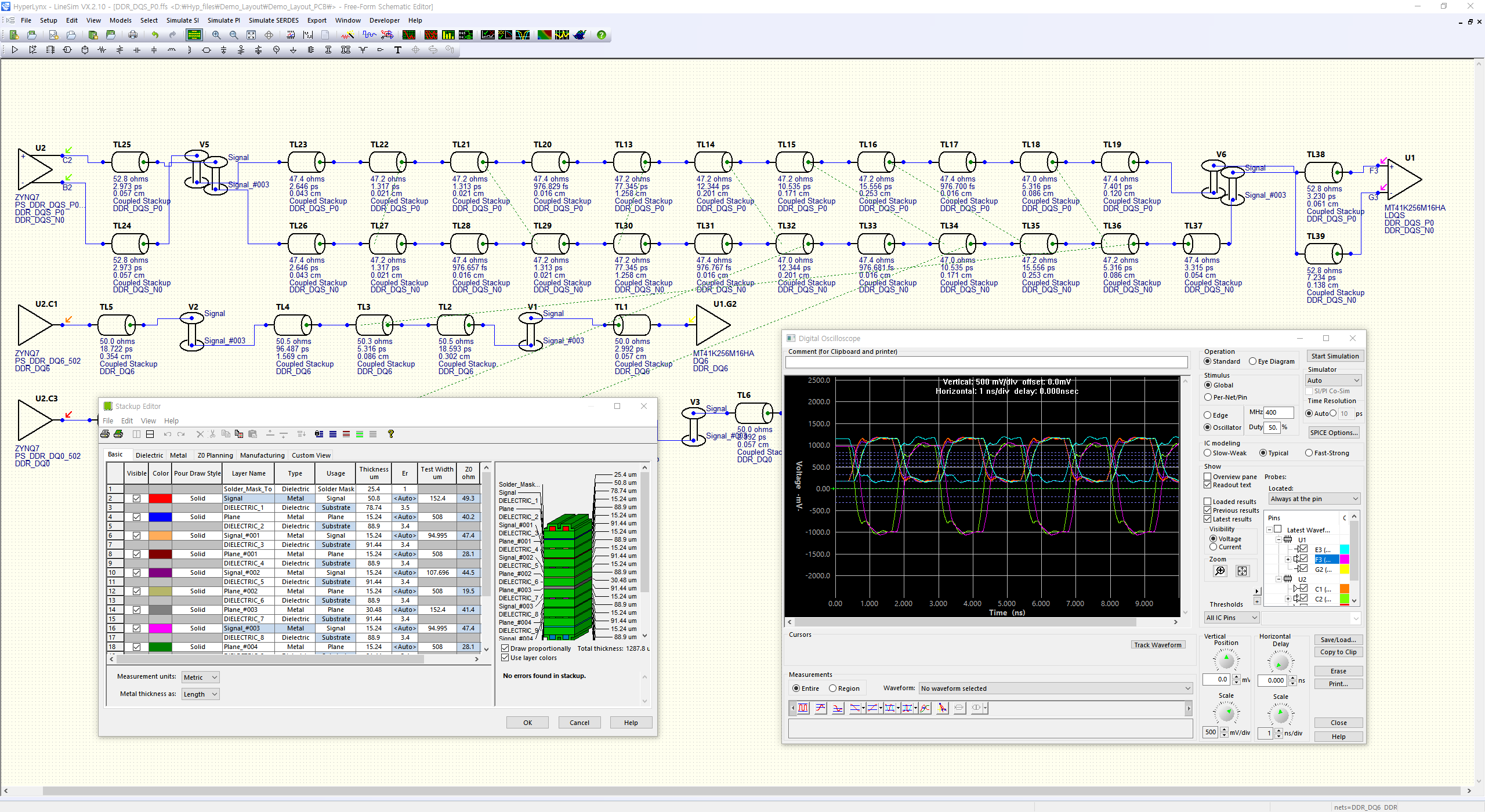

배선 후(Post-route) 검증

HyperLynx post-route (BoardSim) 시뮬레이션으로 board에 대해 signal integrity 및 timing을 분석할 수 있습니다. 부품 배치 후 중요 net을 배선하는 동안, board 설계 완료 후까지의 layout 과정 중 언제든지 분석할 수 있습니다. 이를 통해 PCB 제조 전에 잠재적인 문제를 확인하고 해결하여 voltage 마진 및 timing 마진을 확보할 수 있습니다.

배치 모드 시뮬레이션으로 기본적인 문제에 대해 board 전체를 빠르게 검사

배치 모드 시뮬레이션으로 기본적인 문제에 대해 board 전체를 빠르게 검사

대화식(Interactive) 시뮬레이션의 "what-if" 분석으로 문제 영역을 실시간으로 조사

대화식(Interactive) 시뮬레이션의 "what-if" 분석으로 문제 영역을 실시간으로 조사

Coupling threshold를 사용자가 정의하여 crosstalk의 원인이 되는 net과 coupling 영역의 단면을 실시간으로 확인

Coupling threshold를 사용자가 정의하여 crosstalk의 원인이 되는 net과 coupling 영역의 단면을 실시간으로 확인

다양한 물리적 효과를 켜거나 끄는 기능 지원 : 다양한 현상이 설계 마진에 미치는 영향을 정량화

다양한 물리적 효과를 켜거나 끄는 기능 지원 : 다양한 현상이 설계 마진에 미치는 영향을 정량화

Multi-board 분석 가능 : EBD 및 커넥터 모델 지원

Multi-board 분석 가능 : EBD 및 커넥터 모델 지원

Full-wave 3D field solver와의 인터페이스를 통해 커플링된 via 구조, breakout 및 plane gap과 같은 복잡한 레이아웃 구조 분석 및 추출 가능

Full-wave 3D field solver와의 인터페이스를 통해 커플링된 via 구조, breakout 및 plane gap과 같은 복잡한 레이아웃 구조 분석 및 추출 가능

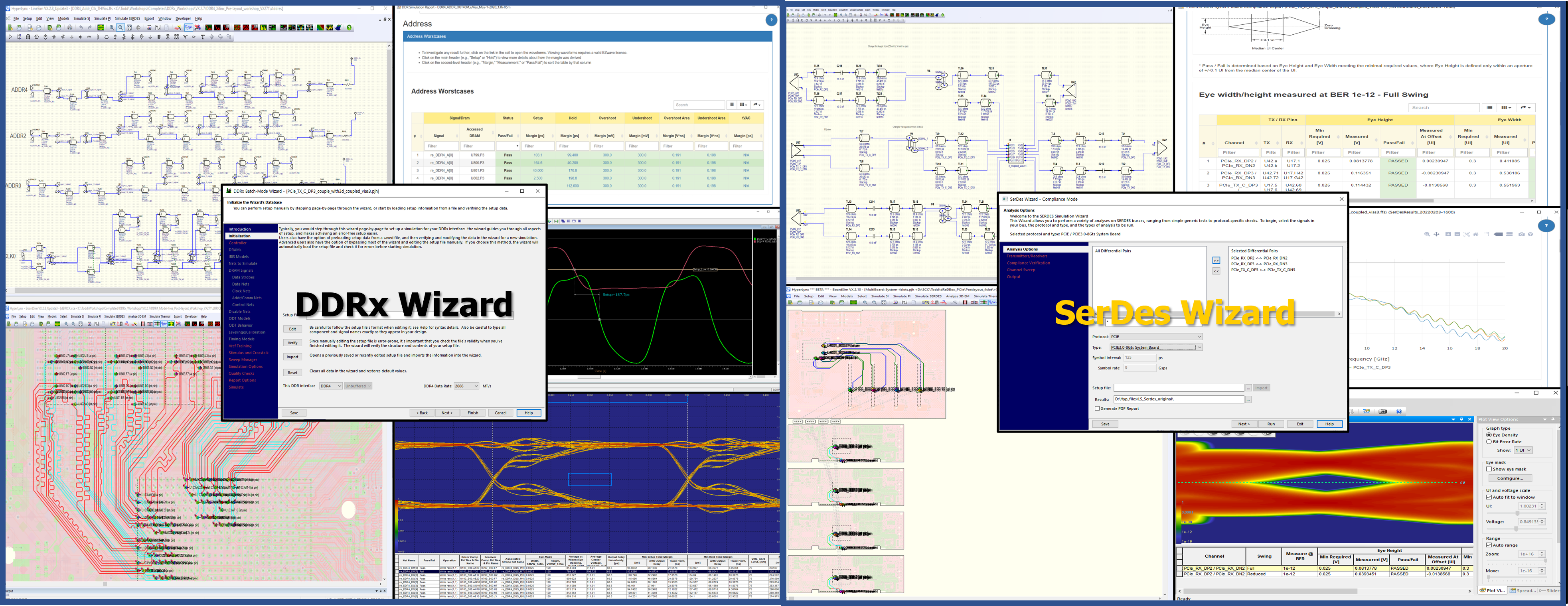

DDRx 및 SerDes 채널 검증

HyperLynx SI는 Wizard를 제공하여 DDRx 인터페이스에 대한 timing/SI 분석 및 Ethernet, PCIe와 같은 SerDes 채널의 규격 분석을 자동화합니다.

DDRx Wizard는 모든 신호에 대해 signal integrity 및 crosstalk simulation을 실행하여 신호 품질 요구 사항을 만족하는지 분석합니다. 그리고 JEDEC 표준을 기반으로 신호들 간 timing을 측정한 후, derating 및 output skew 보상 등을 고려하여 timing 마진을 분석합니다. 옵션인 power-aware 분석 기능을 사용하면 시스템 설계 마진에 대한 드라이버 SSO/SSN 및 비이상적인 return path의 영향을 분석할 수 있습니다.

Timing/SI 마진 분석 결과는 HTML report에 data read/write, address, clock/DQS 등 여러 탭으로 나뉘어 출력되며 측정값을 클릭하면 waveform viewer/eye diagram viewer에서 해당 신호의 waveform/eye plot을 확인할 수 있습니다.

SerDes Compliance Wizard는 Ethernet, PCIE, OIF-CEI, USB 등의 180개 protocol에 대하여 frequency-domain mask, time-domain mask, COM(Channel Operating Margin) 및 JCOM 분석을 지원합니다. 분석 결과 및 표준 준수 여부는 HTML report에 출력되며 그 외에도 HTML report에 eye density plot, TDR impedance plot, frequency domain plot 등이 출력됩니다.