본문

TIMING

디자인에서 대부분의 길이 제약 조건은 timing 필요성에서 비롯됩니다. Timing 필요성은 데이터가 특정 간격으로 receiver에서 처리된다는 사실로부터 비롯됩니다. 시스템이 데이터가 필요한 때에 데이터가 receiver에 없으면 시스템이 작동되지 않습니다.

버스 타이밍 구조에는 common clock 및 source synchronous 이렇게 두 가지 주요 유형이 있습니다. 이로 인해 최소/최대 및 길이 매칭과 같은 두 가지 유형의 레이아웃 제약이 생깁니다. 최소 및 최대 delay 제약은 공통 common clock bus 구조로부터 생성됩니다.

예를 들어, PCI의 경우 common clock을 이용하여 transmitter에서 데이터를 보내고 receiver에서 데이터를 수신합니다. 데이터가 너무 일찍 도착하지 않게, 또는 hold-time 요구 사항을 위반하지 않도록 최소 길이 제약 조건을 만들어야 합니다. 마찬가지로 데이터가 너무 늦게 도착하지 않도록 최대 길이 제약 조건이 만들어집니다. 이러한 제약 조건은 단순히 선의 길이에만 근거하지 않습니다. Receiver loading 및 신호 품질 문제와 같은 다른 많은 고려 사항은 전송된 데이터가 receiver에서 유효할 때를 결정하므로 적절한 신호 분석은 이러한 길이를 적절하게 계산하는 데 매우 중요합니다.

일치된 delay 제약 조건은 source-synchronous 버스에서 발생합니다. DDRx와 같은 버스는 receiver에서 데이터를 판단하기 위해 데이터와 함께 clocking 신호 또는 "strobe"를 전송합니다. 이는 driver와 receiver 간 복잡한 timing 관계를 없애고 strobe와 date의 일치만 요구합니다. 일반적으로 이러한 interface에는 데이터가 유효한 시점을 결정하는 신호 품질과 같은 다른 문제가 있습니다. 이러한 버스에 대한 주요 timing 제약은 일치된 delay 제약 조건이며 버스 속도 또는 신호 품질 문제가 증가함에 따라 더욱 엄격해지고 있습니다.

CROSSTALK

Layout의 또 하나의 중요한 제약 조건은 trace간 간격입니다. 이것은 신호 사이에서 발생하는 crosstalk의 양에 의해 결정됩니다. Driver의 edge rate, board stackup, trace간의 병렬 처리 양 및 trace 간의 간격을 포함하여 여러 요인이 crosstalk에 영향을 미칩니다.

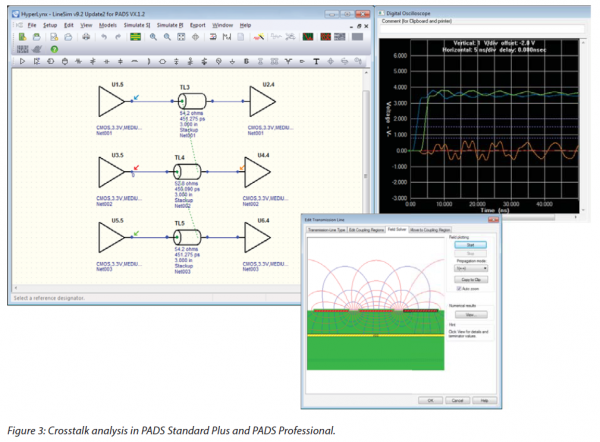

Crosstalk는 신호 품질과 timing에 모두 영향을 미치며 측정한 net에 허용되는 crosstalk 양은 시뮬레이션을 통해 결정할 수 있습니다. Crosstalk 시뮬레이션의 예가 그림 3에 나와 있습니다.

Crosstalk 분석은 일반적으로 "victim" trace와 두 개의 "aggressor" trace로 구성됩니다. 더 많은 aggressor net이 포함될 수 있지만, 대부분의 경우 crosstalk의 95 %는 가장 가까운 두 aggressor net에서 발생됩니다. HyperLynx SI에서 Driver 및 receiver의 모델, board stackup을 설정하고 trace 사이의 간격을 수정하여 허용되는 crosstalk 정도를 결정할 수 있습니다. 서로 평행한 trace의 길이를 수정하고 그 효과도 확인할 수 있습니다. 이러한 분석의 결과로 trace간 간격 규칙을 만들 수 있습니다. 간격 규칙을 충족할 수 없거나 layout에서 더 큰 유연성을 허용하려는 경우, 더 엄격한 간격 및 최대 병렬 처리 제약 조건으로 규칙을 만들 수 있습니다. 이러한 두 제약 조건은 crosstalk 분석을 통해 만들 수 있으며 요구 사항이 변함에 따라 수정할 수 있습니다.

POST-ROUTE VERIFICATION

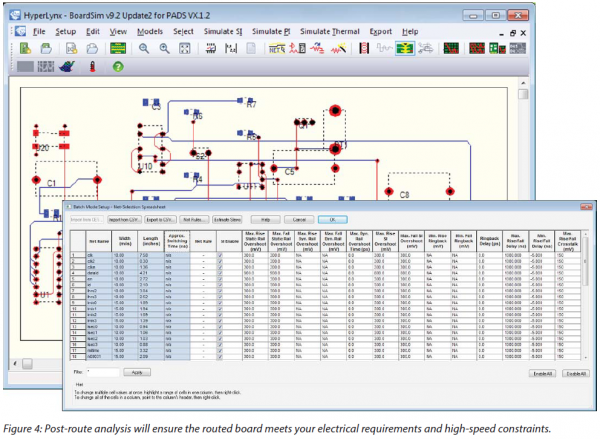

필요한 모든 routing 제약 조건을 만들고 이 제약 조건을 사용하여 board를 routing 한 후에는 board가 원래의 전기적 요구 사항을 충족하는지 확인하는 것이 좋습니다. 충족 여부를 확인할 좋은 방법은 board 상의 모든 net에 대해 post-route analysis를 진행하는 것입니다.

그림 4는 HyperLynx의 batch mode wizard의 예제를 보여줍니다. 그림 4처럼 PADS에서 HyperLynx로 layout data를 export하여 직접 시뮬레이션을 진행하고 overshoot, delay 및 crosstalk 제약 조건에 대해 설계를 검증할 수 있습니다. 이러한 제약 조건을 위반하는 net이 발견되면 이러한 net을 한 번에 한 net씩 시뮬레이션하여 자세히 살펴볼 수 있습니다.

Post-route analysis는 설계 주기 초기에 수행되는 pre-route, 즉 "what-if" 분석을 보완합니다. 이것은 고속 bus를 분석하기 위해 수행되는 일련의 작업 중 하나의 단계입니다. 이러한 유형의 분석 및 결과로 생성된 제약 조건 없이는 현대 디지털 시스템은 오늘날의 비용, 크기 및 성능 요구를 충족 시키도록 설계 될 수 없습니다.

▷ 원문보기 : Three Things to Consider When Designing Electronic Products with High-Speed Constraints

등록된 댓글이 없습니다.