본문

1. Constraint Management

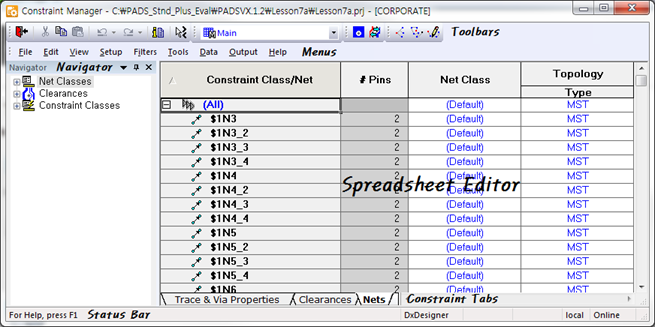

1) Constraint Manager 실행하기

1. xDX Designer를 실행하고 C:/PADS_Stnd_Plus_Eval/PADSVX.1.2/Lesson7a 폴더에 있는 Lesson7a.prj 파일을 오픈 합니다.

2. Main 툴바에 있는 Constraint Manager 아이콘을 클릭합니다.

2) Constraint Manager 환경 설정하기

1. Constraint Management와 Schematic, Layout 환경을 연동하기 위해 File 툴바에 있는 Cross Probing 아이콘을 클릭합니다.

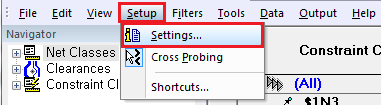

2. [Setup] – [Settings…]를 클릭하고, Settings 창이 열리면 Display 탭으로 이동합니다.

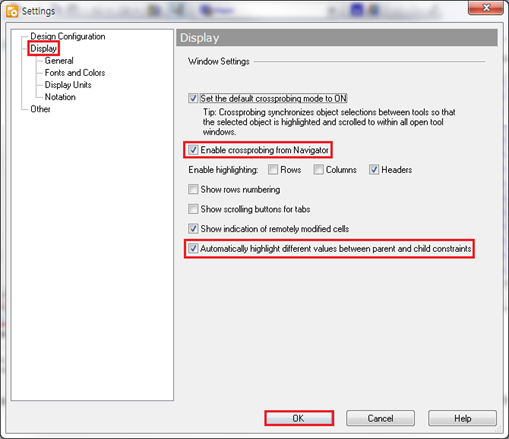

3. Enable crossprobing from Navigator와 Automatically highlight different values between parent and child constraints를 체크하고 OK하여 적용합니다.

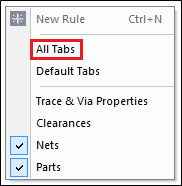

4. Constraint Manager 창으로 돌아와 빈 공간에서 마우스 우 클릭한 후, All Tabs를 클릭하여 모든 스프레드 시트를 표시합니다.

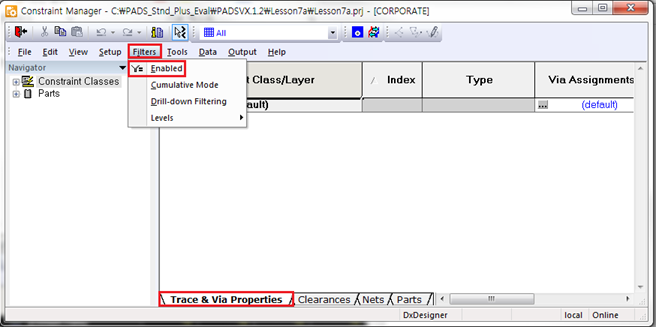

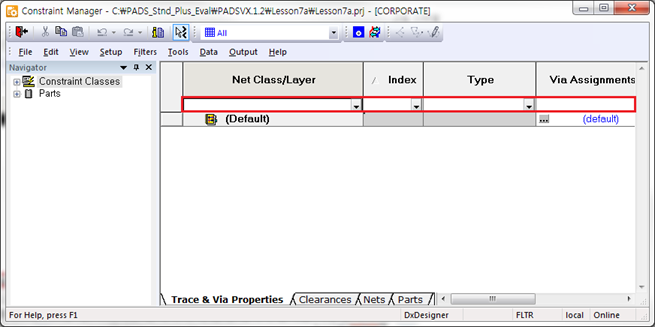

5. Trace & Via Properties 탭을 클릭하고 [Fillers] – [Enabled]를 선택하여 각 행에 대하여 필터를 적용합니다.

6. 다른 탭에도 필터를 적용해 봅니다.

2. 보드 정보 얻어 오기

1) PCB 디자인 생성하기

1. xDX Designer로 돌아와 Main 툴바에 있는 Layout 아이콘을 클릭합니다.

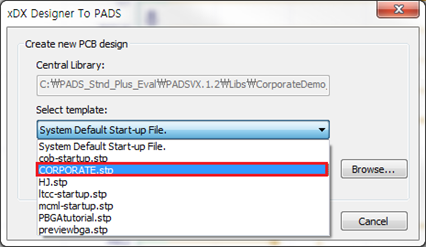

2. xDX Designer to PADS 창이 열리면 Select Template 리스트에서 COPPERATE.stp Start-UP 파일을 선택하고 OK합니다.

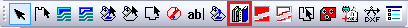

3. PADS Layout 창이 열리면 Standard 툴바에서 Drafting 툴바 아이콘을 클릭합니다.

4. Drafting 툴바에 있는 From Library 아이콘을 클릭합니다.

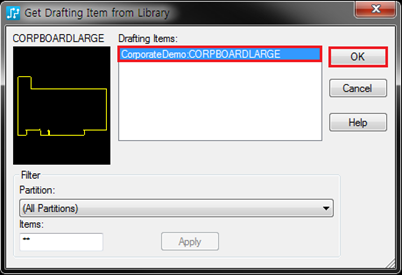

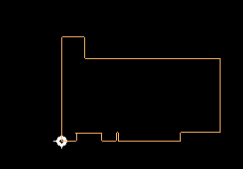

Getting Drafting Item From Library 창이 열리고 PCB 보드 아웃라인인 CORPERATE 표시됩니다. 선택 후, OK합니다.

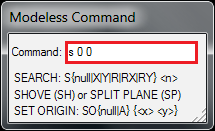

5. Modeless Command 's 0 0'을 입력하고 Space Bar를 눌러 보드 아웃라인을 원점에 위치시킵니다.

6. 위의 그림과 같이 보드 아웃라인이 추가 되었다면 이제, layer stackup 정보와 via padstack 정보를 확인해 볼 것입니다.

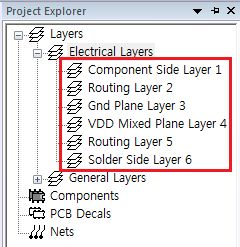

먼저, 좌측에 있는 Project Explorer 창에서 Layers를 더블 클릭하고 Layers 아래에 펼쳐진 Electrical Layers를 더블 클릭합니다.

2개의 Plane layer(Layer 3-4)를 포함하여 총 6층으로 이루어진 보드라는 것을 확인할 수 있습니다.

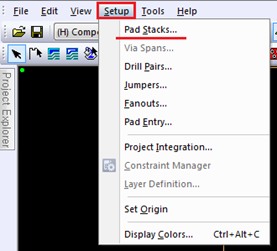

7. [Setup] – [Pad Stacks]를 클릭하고 Pad Stacks Properties 창이 열리면 PAD Stack Type에서 Via를 선택하여 Via Padstack 정보를 확인합니다.

Note. Pad Stacks Properties 창에서 via padstack을 추가하거나 삭제하거나 수정할 수 있습니다.

2) Back Annotating to Constraint Management

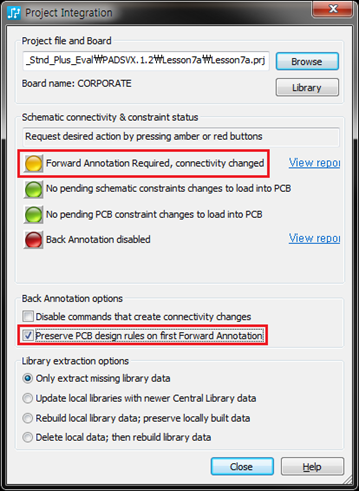

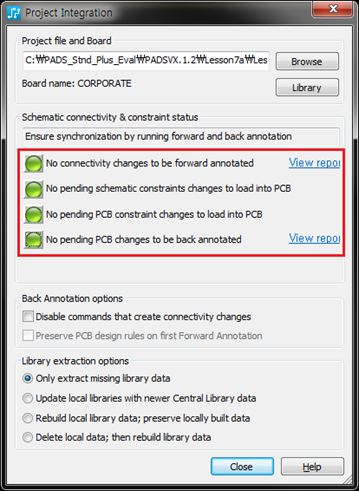

1. PADS Layout 창으로 돌아와, [Setup] – [Project Integration]을 선택합니다.

2. Project Integration 창이 실행되면, Preserve PCB design rules on first Forward Annotation 을 선택하고 노란색 버튼을 클릭합니다.

3. Schematic connectivity & constraint status가 Update된 후, 새롭게 표시된 노란색 버튼을 클릭합니다

4. Schematic connectivity & constraint status가 모두 초록색 버튼으로 Update됩니다.

이는, Shematic 데이터와 Layout 데이터가 모두 동기화 되었음을 의미합니다.

5. Project Integration 창을 종료하고 [File] – [Save]를 눌러 CORPERATE.pcb를 저장합니다.

[File] – [Exit]를 눌러 Layout을 종료하고 xDX Designer로 돌아가 Constraint Manager를 실행합니다.

3) Project Constraints 확인하기

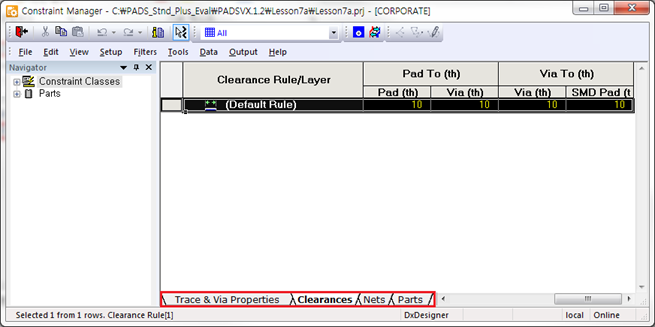

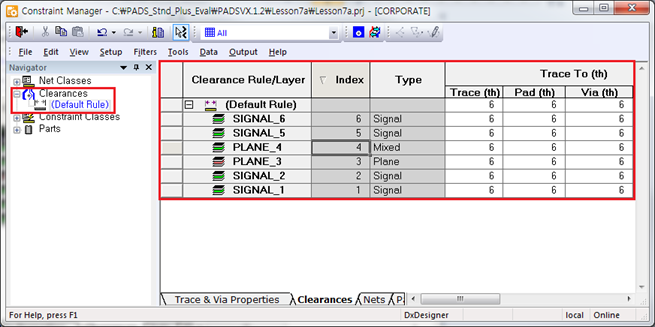

1. Navigation 창에서 Clearance 탭의 [+]를 클릭하고 Clearance 아래 표시된 (Default Rule)을 선택합니다.

설정된 Clearance Rule이 Layer 별로 화면에 표시됩니다.

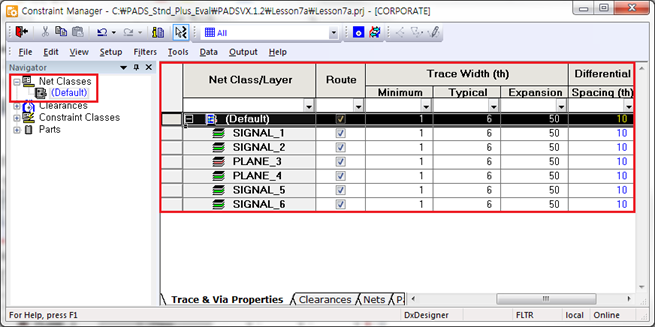

2. Navigation 창에서 Net Classes아래 표시된 (Default)를택합니다.

3. Net Class 생성하기

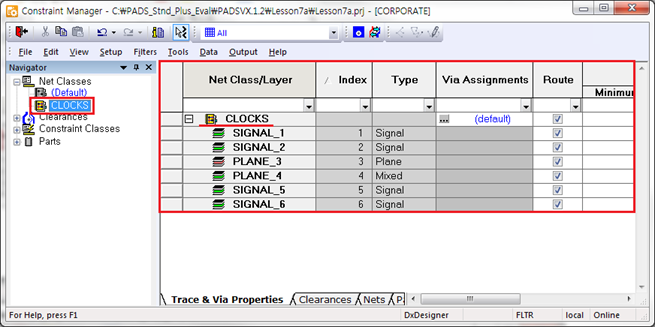

1) Navigator 창에서 Net Class 생성하기

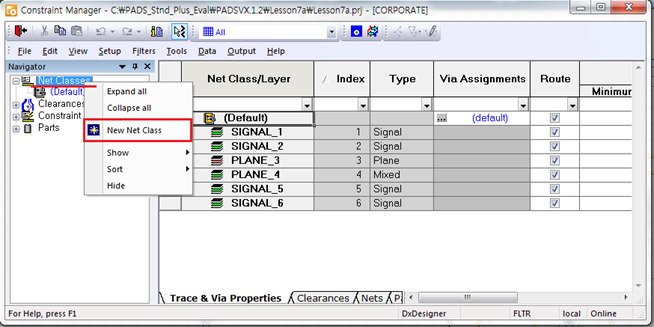

1. Navigator 창의 Net Classes을 선택하고 마우스 우 클릭한 후, New Net Class를 선택합니다.

2. 새로운 Net Class가 생성되고 Name 부분에 'CLOCKS'라고 입력하고 클릭합니다.

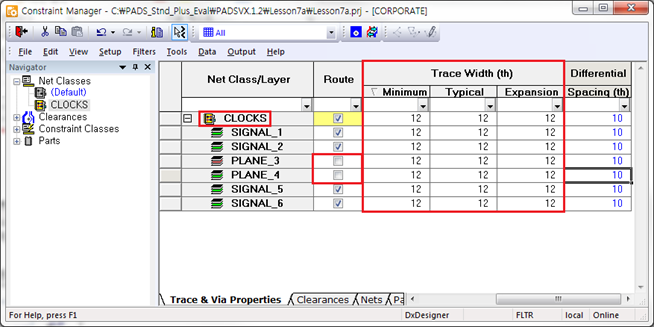

3. CLOCKS Net Class를 아래와 같이 수정합니다.

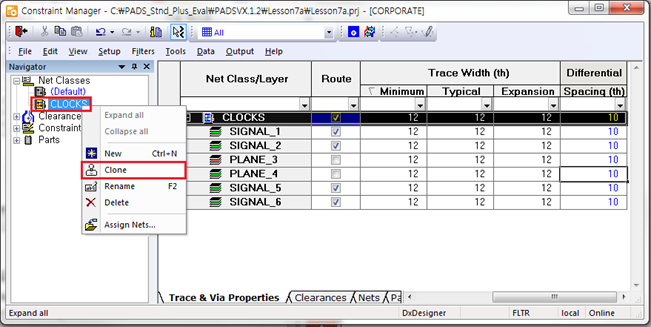

2) Net Class 복제하기

1. Navigator 창에서 CLOCKS를 선택하고 마우스 우 클릭한 후, 'Clone'을 클릭하여 CLOCKS를 복제합니다.

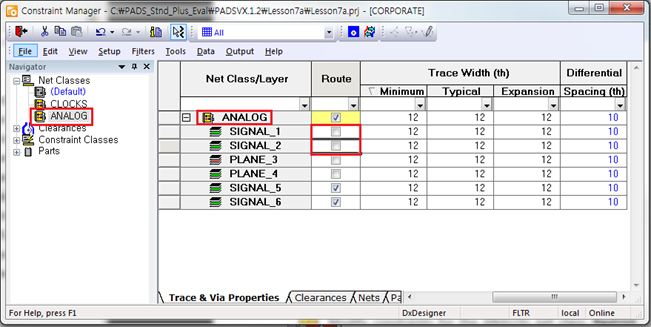

2. 복제된 Net Class를 선택하고 마우스 우 클릭한 후, Rename 메뉴를 눌러 'ANALOG'로 Net Class 이름을 변경합니다.

ANALOG Net Class를 아래와 같이 수정합니다.

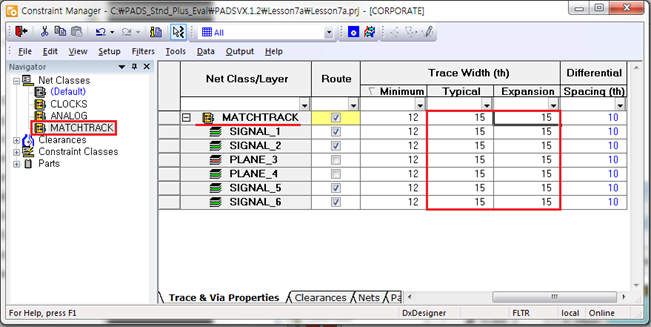

3. CLOCKS Net Class를 복제한 후, 이름을 'MATCHTRACK'로 변경하고 Net Class를 아래와 같이 수정합니다.

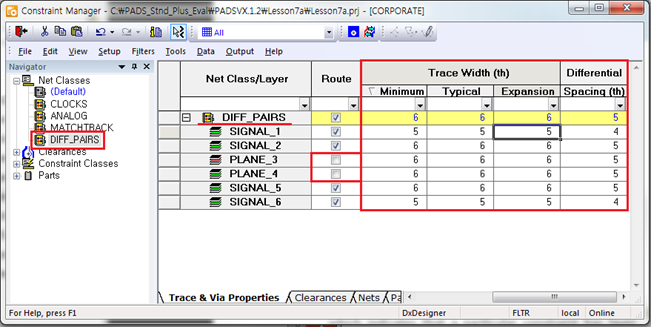

3) Diff Pairs Net Class 생성하기

1. 이름이 'DIFF_PAIRS'인 새로운 Net Class를 생성하고 Net Class는 아래와 같이 설정합니다.

3. Net에 Net Class 지정하기

1) Net에 Net Class 지정하기

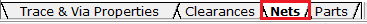

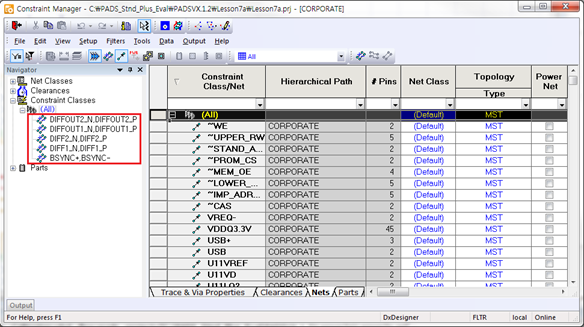

1. 하단에 있는 Nets 탭을 선택합니다.

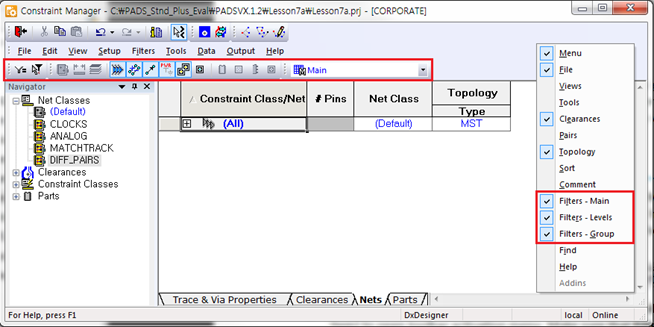

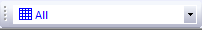

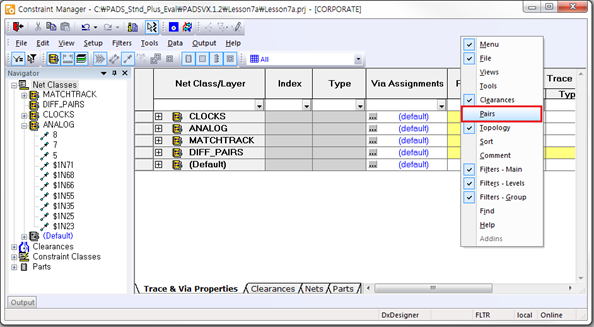

2. 툴바 영역에서 마우스 우 클릭하면 아래 그림과 같은 메뉴 창이 나타납니다.

'Filters-Main', 'Filters-Levels', 'Filters-Group' 툴바를 체크하여 활성화합니다.

3. Filters-Group 툴바의 리스트 중 'All'을 선택하고, Filers-Main 툴바에서 'Enable/Disable Filters' 아이콘을 선택합니다.

- Filters-Group툴바

- Filters-Main 툴바

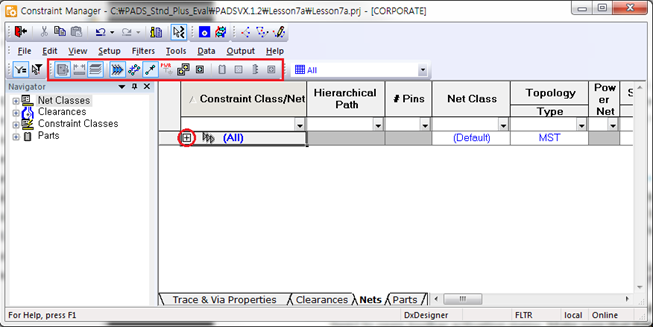

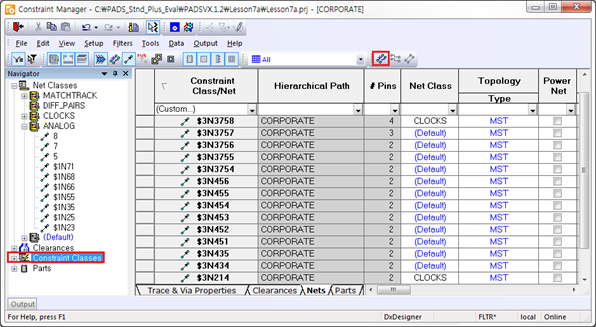

4. Filters-Level 툴바의 Physical Nets 아이콘만 Enable하고, All 옆에 있는 [+] 버튼을 클릭하여 Constraint Class를 포함한 모든 Net를 표시합니다.

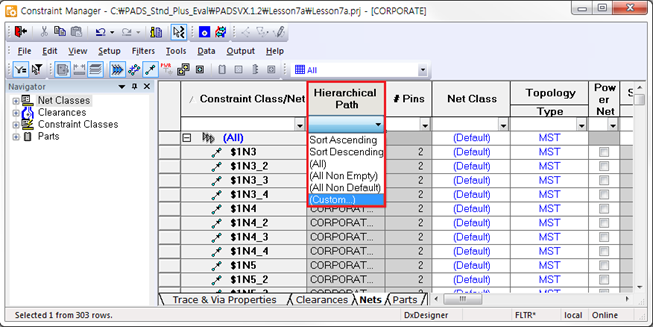

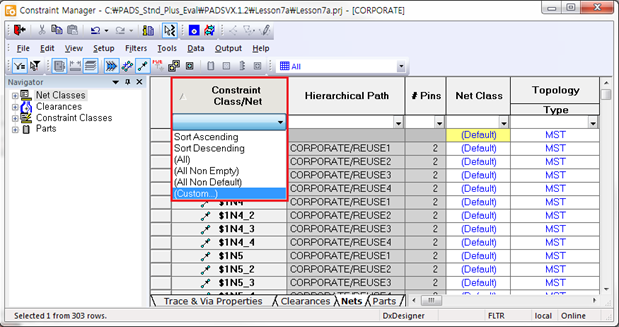

5. Hierarchical Path 리스트 중 '(Custom…)'을 선택합니다.

Custom Autofilter 창이 열리면 CORPORATE/Analog를 입력하고 Apply합니다.

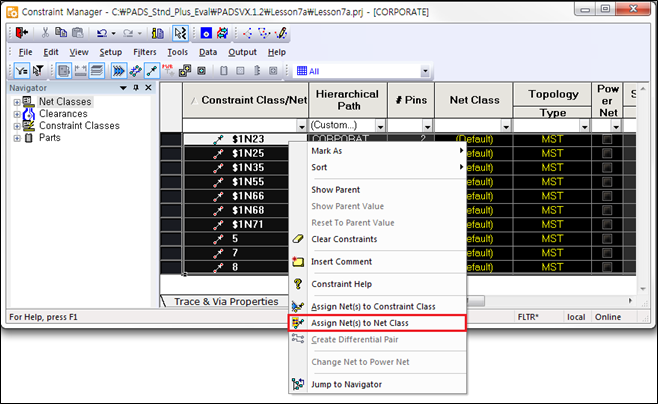

6. 모든 Net를 선택하고 Constraint Class/Net 열에서 마우스 우 클릭하여, Assign Net(s) to Net Class 메뉴를 선택합니다.

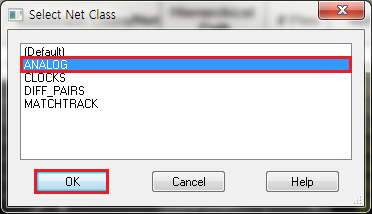

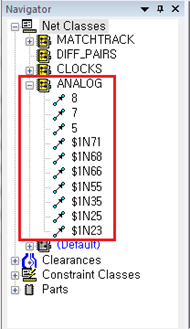

7. Select Net Class 창이 열리면 'ANALOG'를 선택하고 OK하여 선택된 Net에 ANALOG Net Class를 적용합니다.

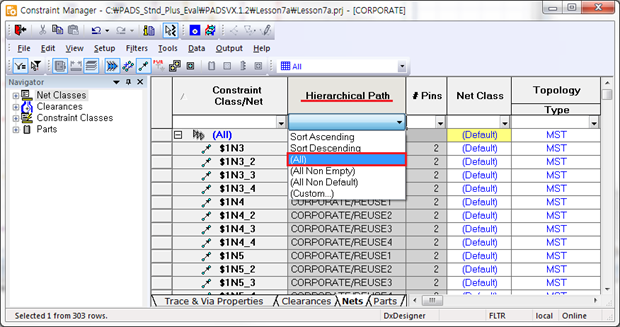

8. Hierarchical Path리스트 중, '(All)'을 클릭합니다.

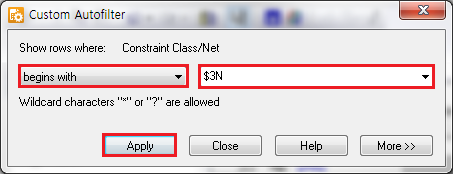

9. Constraint Class/Net 리스트 중 '(Custom)'을 선택하고 Custom Autofilter 창이 열리면 좌측은 'begins with', 우측은 '$3N'을 입력한 후 Apply합니다.

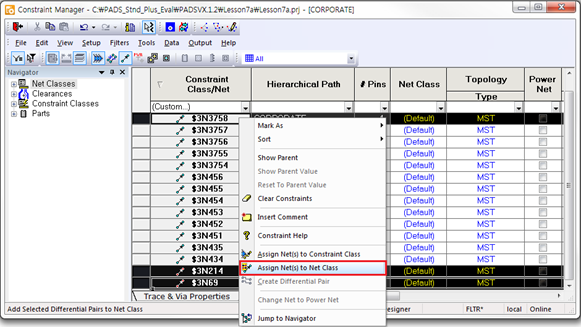

10. '($3N69, $3N214, $3N3758)'을 선택한 후, Constraint Class/Net 열에서 마우스 우 클릭하여 Assign Net(s) to Net Class 메뉴를 선택합니다.

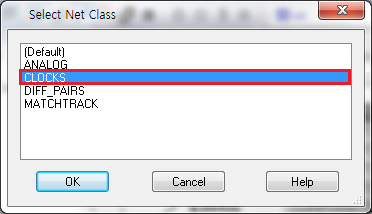

Select Net Class 창이 열리면 'CLOCKS'를 선택하고 OK하여 선택된 Net에 CLOCKS Net Class를 적용합니다.

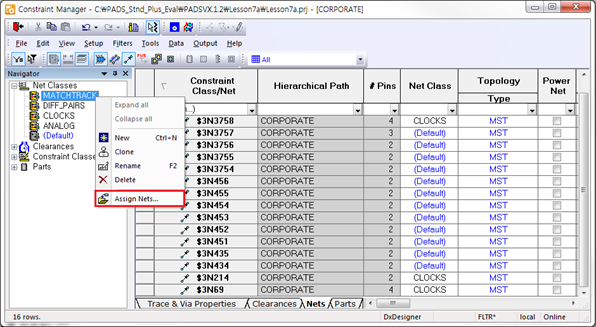

11. Navigator 창에서 MATCHTRACK Net Class를 선택하고 마우스 우 클릭하여 Assign Nets 메뉴를 선택합니다.

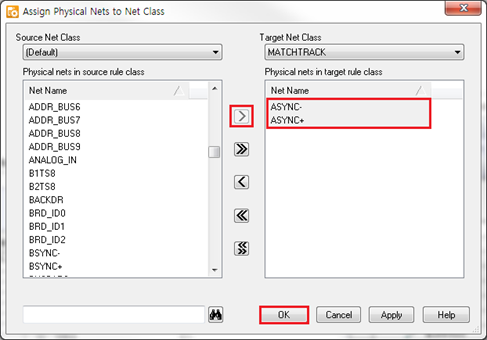

12. Assign Physical Nets to Net Class 창이 열리면 아래와 같이 설정하여, '(ASYNC+, ASYNC-)' Net에 MATCHTRACK Net Class를 적용합니다.

2) Differential Pair 생성하기

1. 툴바 영역에서 마우스 우 클릭 후, Pairs를 선택하여 Pairs 툴바를 Enable합니다.

2. Navigator 창에서 Constraint Classes를 선택하고, Pairs 툴바에서 Auto Assign Differential Pairs 아이콘을 클릭합니다.

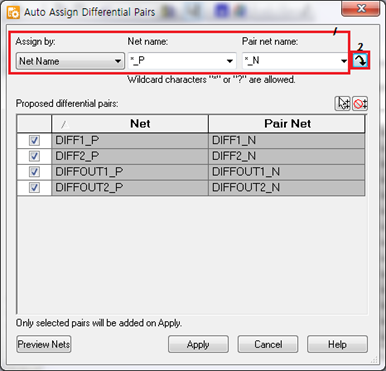

3. Auto Assign Differential Pairs 창이 열리면 아래와 같이 입력 후, Assign Matches 버튼을 클릭합니다.

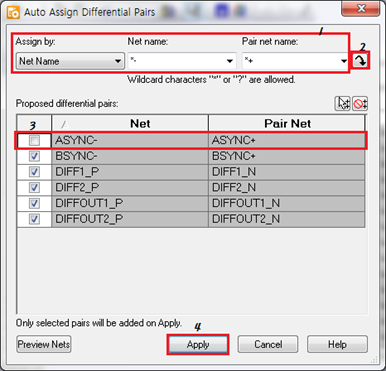

4. Net name과 Pair net name 부분을 아래와 같이 변경한 후, Assign Matches 버튼을 클릭합니다.

Proposed differential pairs 부분에서 (ASYNC-, ASYNC+) 부분의 체크를 해제한 후, Apply합니다.

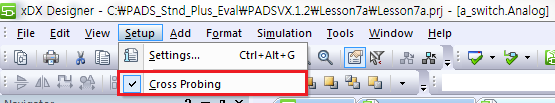

5. xDX Designer 창에서 [Setup – Cross Probing]을 Enable해줍니다.

Note. Cross Probing을 Enable하면, Constraint Manager에서 선택한 것이 동시에 Schematic에서도 선택이 됩니다.

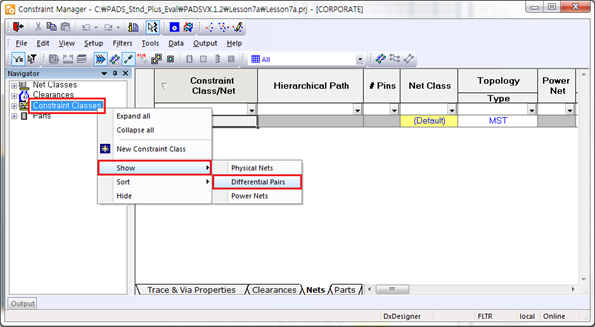

6. Constraint Manager로 돌아와, Navigator 창의 Constraint Classes를 선택하고 마우스 우 클릭하여 Show 메뉴의 Differential Pairs를 선택합니다.

7. Navigation 창에서 Constraint Classes 탭의 [+]를 클릭하고 '(All)' 옆의 [+]를 클릭합니다. 회로에 포함되어 있는 Differential Pair가 모두 보여집니다.

8. Constraint Manager의 Navigator 창에서 '(BSYNC+, BSYNC-)' Differential Pair를 선택하면 Schematic에서도 선택되는 것을 확인할 수 있습니다.

3) Differential Pair에 Net Class 지정하기

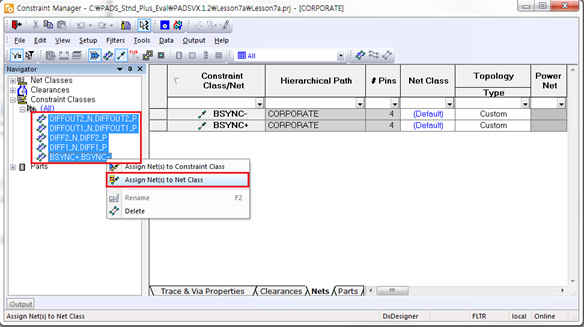

1. Constraint Manager 창으로 돌아와, Constraint Classes 아래에 표시된 모든 Differential Pair를 선택하고 마우스 우 클릭하여 'Assign Net(s) to Net Class'를 선택합니다.

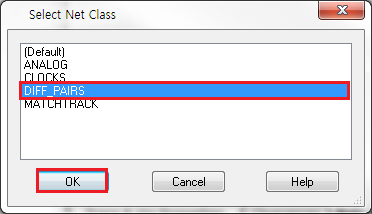

2. Select Net Class 창이 열리면 DIFF_PAIRS Net Class를 선택한 후, OK합니다.

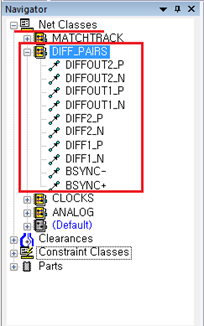

3. 선택한 Net들에 DIFF_PAIRS Net Class가 적용됩니다.

4) Clearance Rule 생성하기

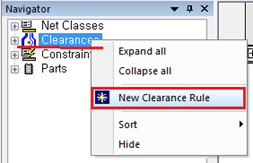

1. Clearances 탭을 선택하고 마우스 우 클릭하여 New Clearance Rule 메뉴를 클릭합니다.

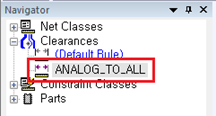

2. 새로운 Clearance Rule이 생성되고 Name 부분에 'ANALOG_TO_ALL'이라 입력하고 클릭합니다.

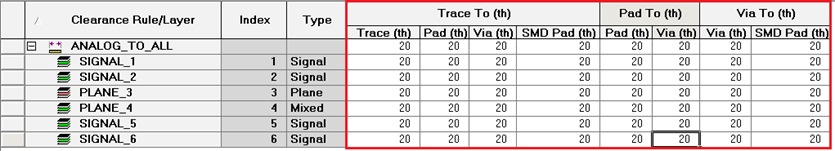

3. 우측의 Clearance 표를 아래와 같이 설정합니다.

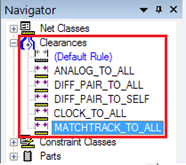

4. 위와 같은 방법으로 4개의 Clearance Rule을 추가로 생성합니다.

- NAME = DIFF_PAIR_TO_SELF, All Value = 10

- NAME = DIFF_PAIR_TO_ALL, All Value = 12

- NAME = CLOCK_TO_ALL, All Value = 20

- NAME = MATCHTRACK_TO_ALL, All Value = 15

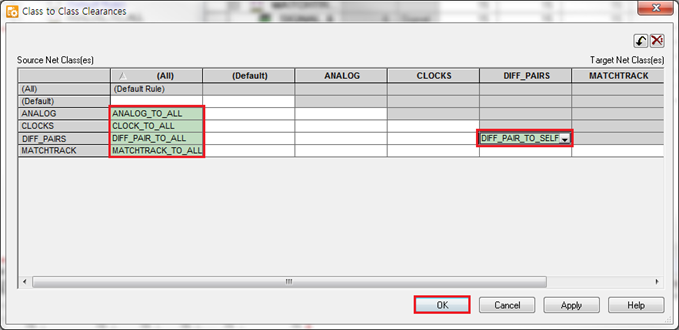

5. Clearance 툴바에서 Class to Class Clearance Rules 아이콘을 클릭합니다.

6. Class to Class Clearance 창이 열리면 아래와 같이 설정 후, OK합니다.

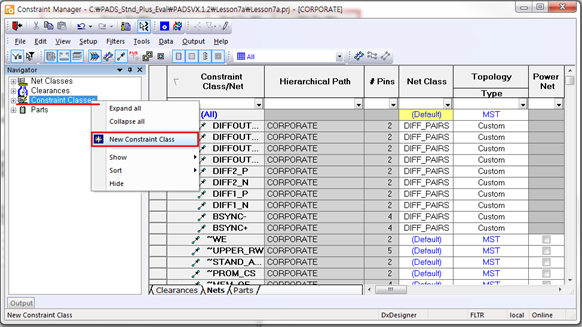

5) Constraint Class 생성하기

1. Constraint Classes탭을 선택하고 마우스 우 클릭하여 New Constraint Class 메뉴를 클릭합니다.

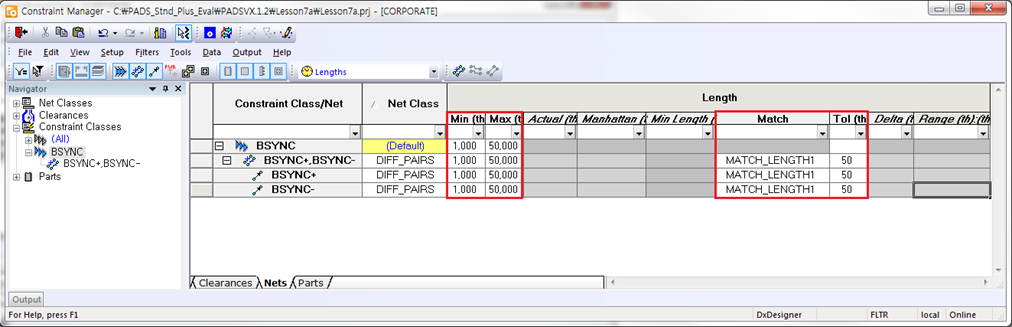

2. 새로운 Constraint Class가 생성되고 Name 부분에 'BSYNC'라 입력하고 클릭합니다.

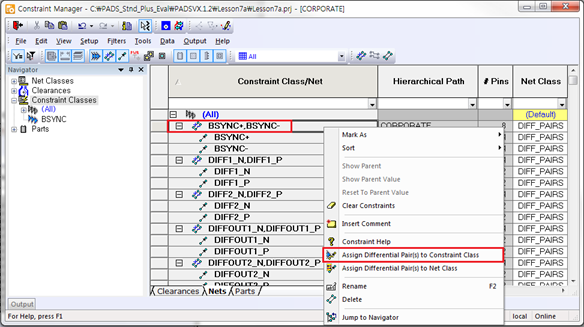

3. Filters-Level 툴바에서 Differential Pairs 아이콘을 클릭하여 Enable합니다.

우측의 표시된 표에서 'BSYNC+, BSYNC-' Differential Pair를 선택하고 마우스 우 클릭하여 Assign Differential Pair(s) to Constraint Class 메뉴를 클릭합니다.

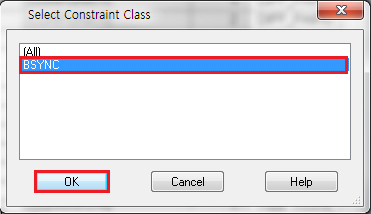

4. Select Constraint Class 창이 열리면 'BSYNC' Constraint Class를 선택하고 OK합니다.

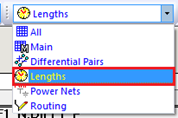

5. Filters-Groups 툴바 리스트 중, 'Length' 옵션을 선택합니다.

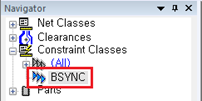

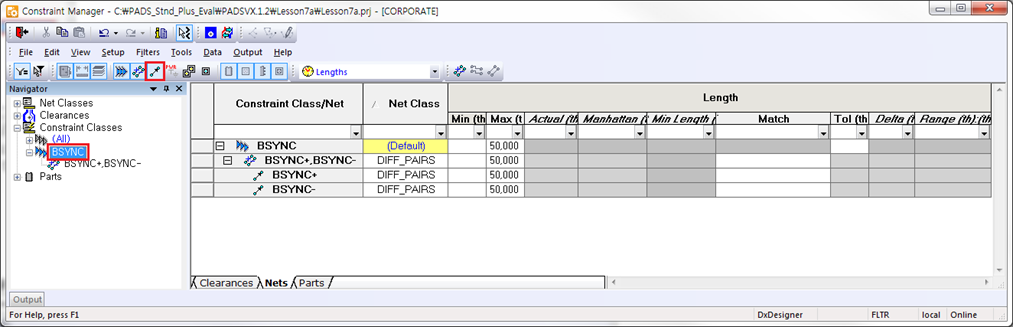

6. Filters-Level 툴바에서 Physical Nets아이콘을 클릭하여 Enable하고 Navigator 창에서 BSYNC Constraint Class를 선택합니다.

7. 'BSYNC' Constraint Class를 아래와 같이 설정합니다.

등록된 댓글이 없습니다.