복잡한 고속 설계의 난제를 지능형 시뮬레이션으로 해결

데이터 전송 속도가 빨라질수록 신호 무결성(SI) 문제는 선택이 아닌 필수입니다. HyperLynx SI는 복잡한 시뮬레이션 환경을 자동화하고 정밀한 분석 결과를 제공하여 PCB 설계의 성공률을 극대화합니다.

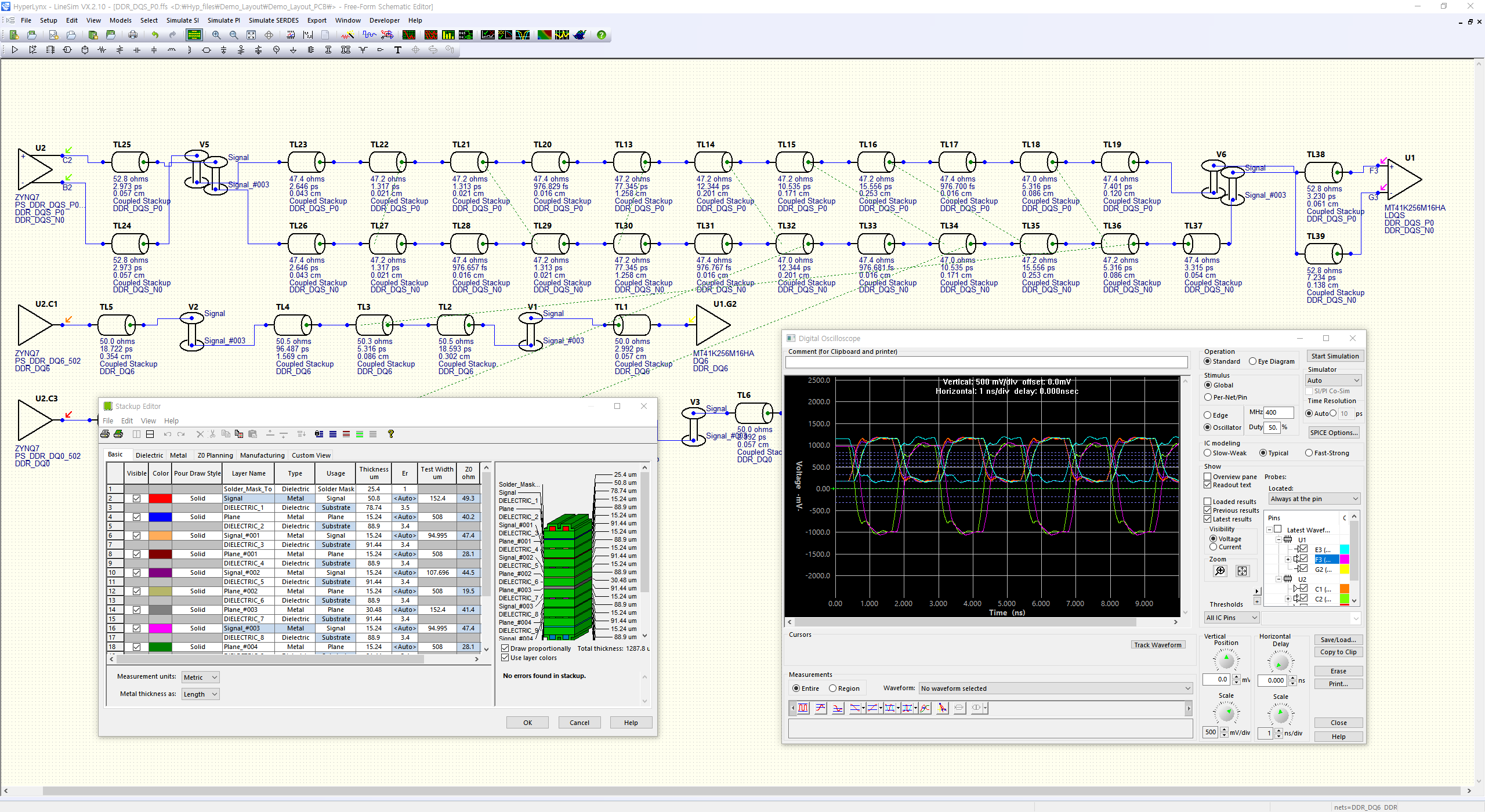

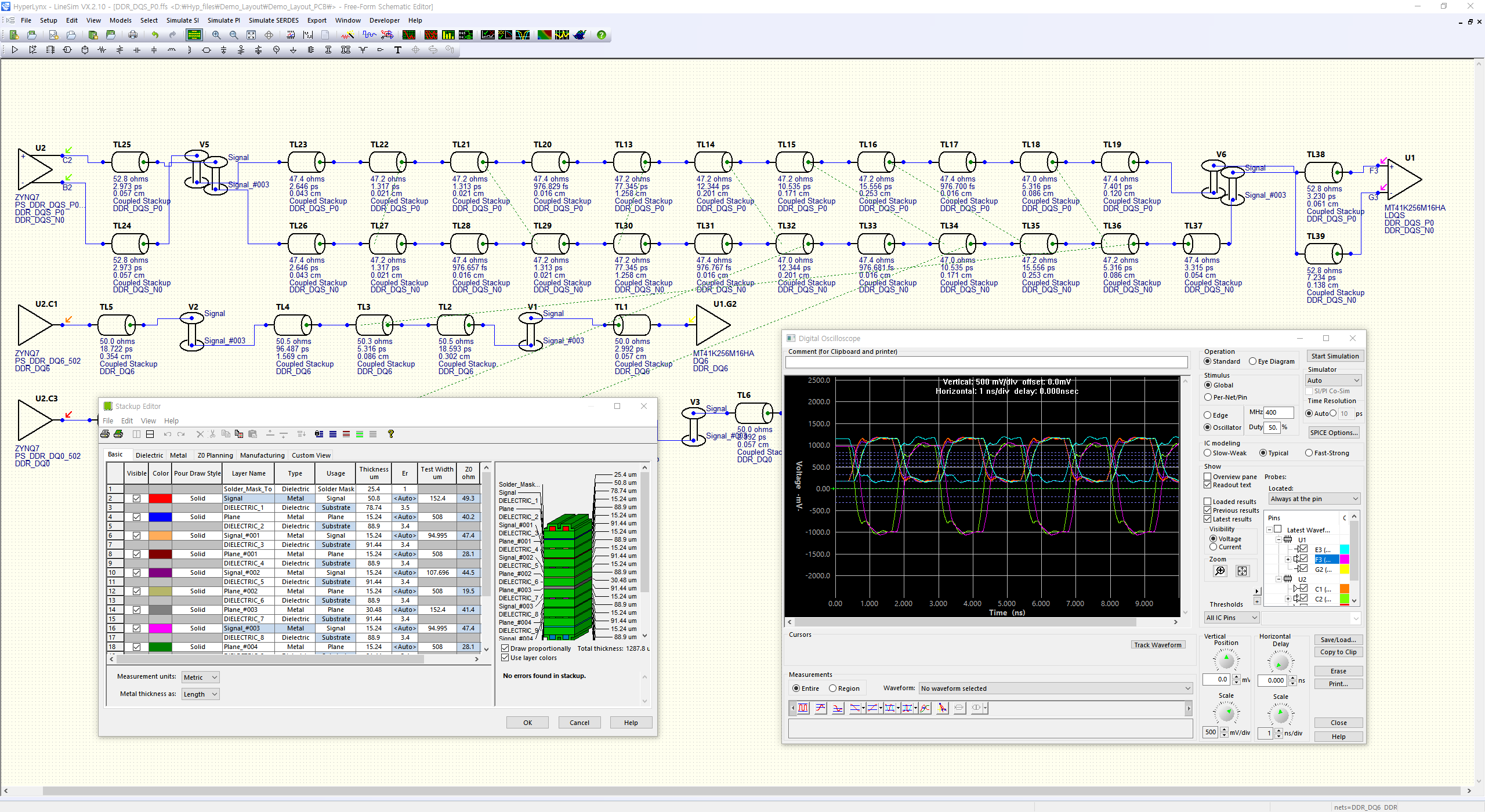

Signal Integrity

Overshoot, Undershoot, Ringing 현상을 시각화하고 최적의 종단 저항 값을 산출하여 신호 품질을 확보합니다.

Power Integrity

DC Drop 및 PDN 임피던스 분석을 통해 전원 노이즈가 고속 신호에 미치는 영향을 통합적으로 검증합니다.

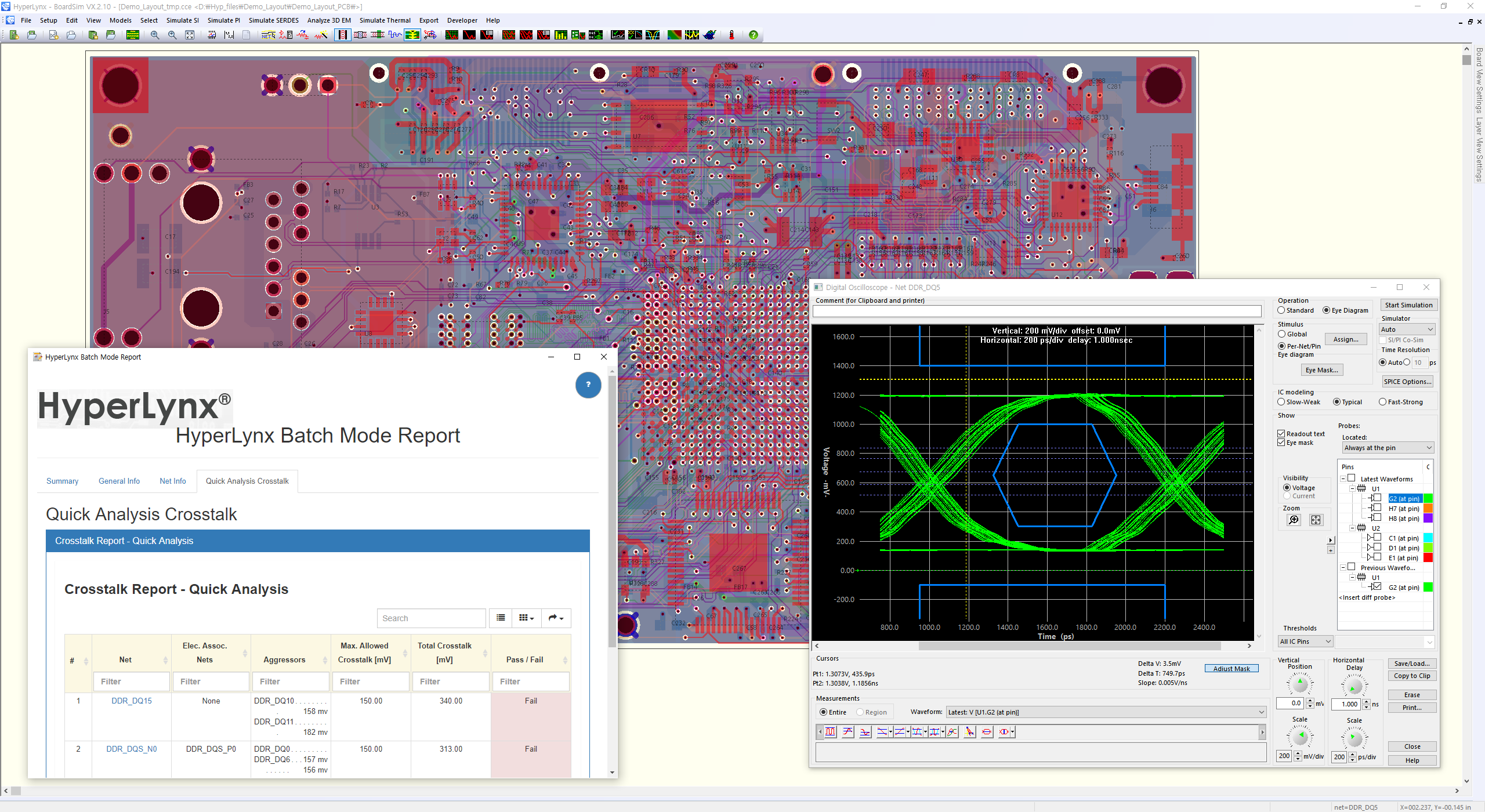

SerDes Compliance

PCIe, USB, Ethernet 등 차세대 인터페이스에 대한 Eye Diagram 분석을 자동화 Wizard로 지원합니다.

Virtual Prototyping

물리적 제작 전 수천 번의 가상 테스트를 통해 재설계 비용을 획기적으로 낮추는 기술력을 제공합니다.

압도적인 정확도의

보드 레벨 검증

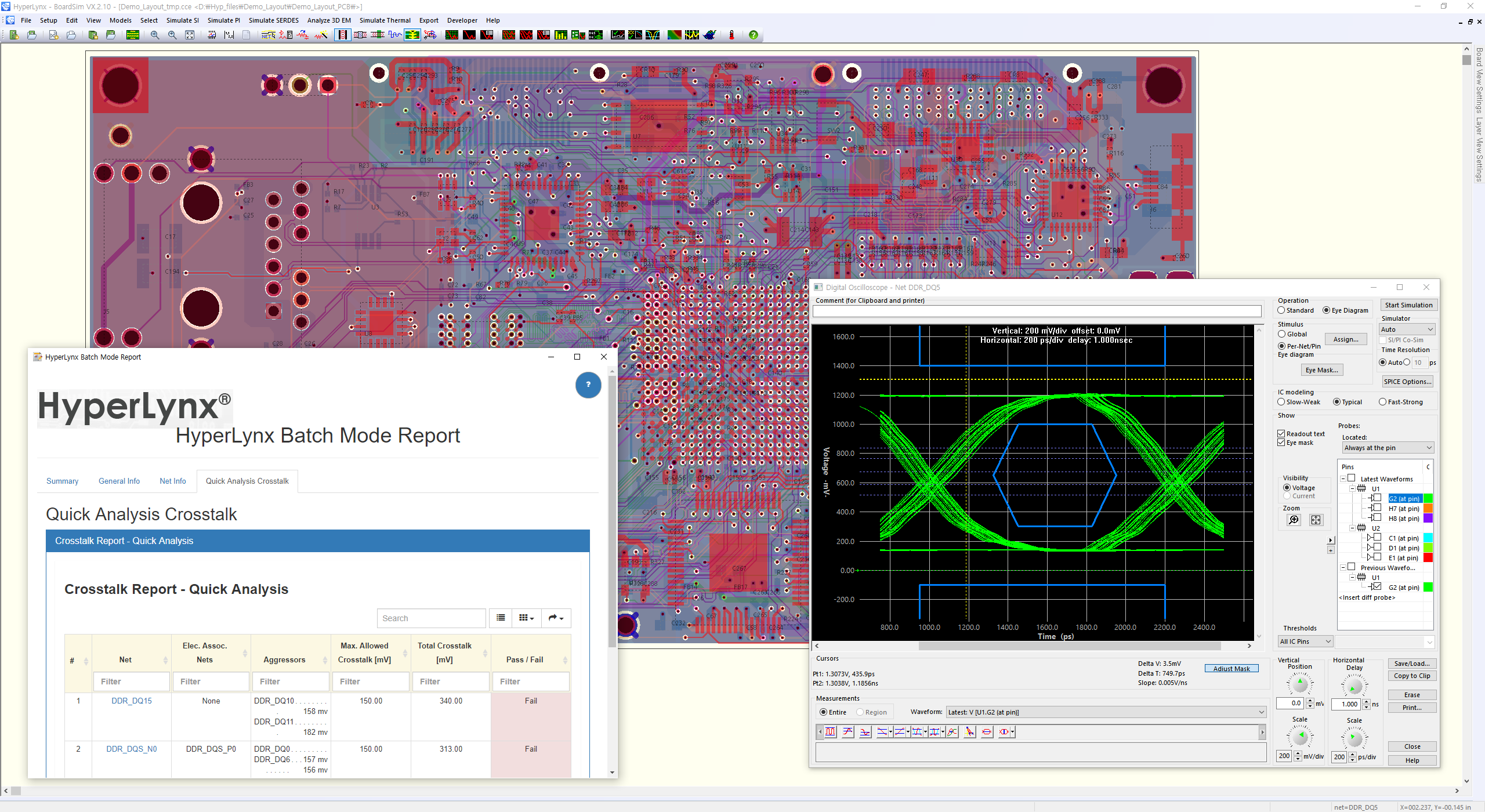

수천 개의 네트를 가진 복잡한 다층 보드에서도 자동화된 배치 시뮬레이션을 통해 결함 영역을 즉시 탐지합니다.

- 3D EM Solver: 비아(Via) 구조와 복잡한 평면 갭의 신호 반사 정밀 모델링

- Batch Simulation: 전체 보드의 모든 네트를 스캐닝하여 잠재 결함 식별

- Full-wave 엔진: 실제 배선 데이터를 기반으로 최종 사인오프 시간 최소화

자동화된 결과 분석 및 리포팅

전문 지식이 부족하더라도 마법사 기반 인터페이스를 통해 효율적인 문서화와 팀 커뮤니케이션이 가능합니다.

- 분석 결과와 파형을 포함한 HTML 형식 자동 저장

- 표준화된 보고서를 통한 유관 부서와의 명확한 의사소통

- 복잡한 분석 과정을 단계별 가이드로 지원하는 Wizard 기능

지원 인터페이스 및 규격

HyperLynx SI는 글로벌 표준의 모든 고속 프로토콜 시뮬레이션을 지원합니다.

| 카테고리 | 지원 프로토콜 및 사양 | 주요 분석 항목 |

|---|---|---|

| Memory | DDR3/4/5, LPDDR4/5, GDDR6, HBM | JEDEC Compliance, Write/Read Leveling |

| SerDes | PCIe Gen 5/6, USB 4, 100G/400G Ethernet | Eye Mask, BER, COM (Channel Operating Margin) |

| General | HDMI 2.1, DisplayPort, MIPI, SATA | Crosstalk, TDR, S-Parameter Extraction |

왜 HyperLynx SI인가?

직관적인 워크플로우

전문가가 아니더라도 복잡한 분석을 쉽게 진행할 수 있는 마법사(Wizard) 기반 인터페이스를 제공합니다.

강력한 자동화 엔진

Batch 시뮬레이션을 통해 전체 보드의 모든 네트를 빠르게 스캐닝하여 잠재적인 SI 결함을 즉시 찾아냅니다.

검증된 정확성

산업 표준 규격을 완벽히 지원하며, 실제 측정값과 높은 상관관계를 보장하는 신뢰성 있는 결과를 제공합니다.

고속 설계의 수준을 글로벌 클래스로 격상하십시오.

HyperLynx SI 전문가의 맞춤형 컨설팅과 정밀한 견적 서비스를 지금 바로 받아보세요.

솔루션 상담 및 견적 신청하기